Tổng Quan Về Verilog HDL

Có thể bạn quan tâm

1. Verilog HDL là gì?

Verilog HDL là một chuẩn "ngôn ngữ mô tả phần cứng" của IEEE, là một ngôn ngữ dạng text thuần túy được sử dụng để mô tả các mạch Số (thậm chí các mạch Số này có thể được hiện thực thành phần cứng).

Verilog HDL được sử dụng để mô hình hóa phần cứng cho cả mục đích synthesis (tổng hợp) và simulation (mô phỏng).

2. Lịch sử Verilog HDL

Ban đầu Verilog HDL (sau này gọi là Verilog cho tiện) được phát minh bởi Getway Design Automation và được giới thiệu lần đầu tiên vào năm 1984. Năm 1989 được mua lại bởi Cadence, sau đó Verilog được phát hành miễn phí. Tổ chức Open Verilog International (OVI) đã được thành lập nhằm kiểm soát các đặc tả ngôn ngữ. Năm 1995, OVI Verilog đã được thông qua bởi IEEE như là một chuẩn mới của hiệp hội. Năm 2001, IEEE đã giới thiệu phiên bản mới của Verilog và hiện tại đang là phiên bản được sử dụng rộng rãi nhất - Verilog HDL 2001. Năm 2005, SystemVerilog được giới thiệu như là một sự mở rộng của Verilog với các kỹ thuật kiểm tra hướng đối tượng. Năm 2009, IEEE kết hợp chuẩn Verilog với SystemVerilog thành một chuẩn duy nhất: IEEE 1800-2009. Và hiện tại, chuẩn mới nhất là: 1800-2012 - IEEE Standard for SystemVerilog--Unified Hardware Design, Specification, and Verification Language.

3. Các thuật ngữ quan trọng trong Verilog HDL

Xuyên suốt chuỗi bài này và các bài viết khác liên quan đến Verilog, bạn có thể bắt gặp nhiều thuật ngữ mới. Có 4 thuật ngữ quan trong sau đây:

- HDL: Là viết tắt của Hardware Description Language (ngôn ngữ mô tả phần cứng) dựa trên ngôn ngữ lập trình mà được sử dụng cho việc mô hình phần cứng. Khi bạn sử dụng HDL, có hai cách để bạn mô hình hoá mạch số của bạn, đó là Behavior Modeling (mô hình hành vi) và Structural Modeling (mô hình cấu trúc).

- RTL: Là viết tắt của Register Transfer Level, là một thuật ngữ thông dụng dùng để mô tả phong cách Behavior Modeling mà định nghĩa mối quan hệ giữa các input và output theo các thao tác data-flow (dòng dữ liệu) bên trong mô hình phần cứng của bạn. Cấu trúc RTL là có thể tổng hợp được. Synthesis (tổng hợp) đề cập đến cả việc chuyển đổi và việc tối ưu HDL code thành mạch số theo một công nghệ cụ thể. Một số ví dụ điển hình là Lookup Table và Flip-Flop của FPGA. RTL Synthesis đơn giản chỉ đề cập đến việc chuyển đổi mô hình RTL.

- Behavior Modeling: Là một thành phần được mô tả bởi đáp ứng Input/output của nó.

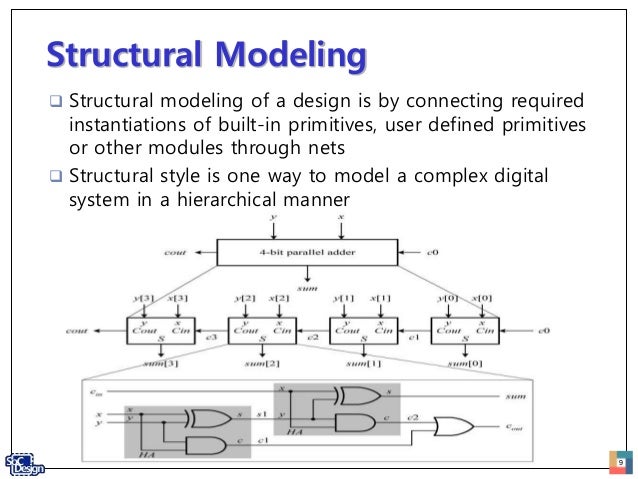

- Structural Modeling: Là một thành phần được mô tả bởi các kết nối mức thấp giữa các thành phần con của mạch.

4. RTL Synthesis

Hình dưới minh hoạ tiến trình tổng hợp RTL. Ở bước đầu tiên, synthesis engine chuyển đổi code của bạn thành phần cứng bằng cách sử dụng các thành phần kiến trúc được có sẵn trong thư viện của bạn. Sau đó nó sẽ đến bước tối ưu hoá để đảm bảo bạn có mô tả mạch có thể hiện thực tốt nhất.

5. Behavior Modeling

Trong Behavior Modeling, bạn sẽ mô tả chức năng của mạch chứ không phải cấu trúc của mạch. Hành vi output được mô tả theo mối quan hệ với các input. Phía dưới là một ví dụ về HDL code hướng hành vi. Ở đây là một D-FF viết theo ngôn ngữ Verilog ở mức hành vi (Behavior). Trong Verilog có nhiều mức khác nhau để thiết kế mạch tích hợp như: Register Transfer Level (RTL), mức GATE và một số mức khác. Ở đây mình sẽ giới thiệu và hướng dẫn các bạn theo mức hành vi (Behavior). Còn các mức khác các bạn có thể tham khảo trên mạng để hiểu rõ hơn.

6. Structural Modeling

Theo hướng cấu trúc, cả chức năng và cấu trúc của mạch được xác định rõ, các kỹ sư viết HDL code sẽ gọi ra các thành phần phần cứng thực tế và nối dây chúng lại với nhau. Các thành phần phần cứng có thể đơn giản chỉ là cổng AND hoặc cổng OR, hay thậm chí cũng có thể là một module biểu diễn các mức trừu tượng khác. Trong một thiết kế hiện đại điển hình, bạn sẽ tìm các thành phần của cả mô hình hướng hành vi và mô hình hướng cấu trúc.

Nguồn: Thegioivimach

Bạn Có Đam Mê Với Vi Mạch hay Nhúng - Bạn Muốn Trau Dồi Thêm Kĩ Năng

Mong Muốn Có Thêm Cơ Hội Trong Công Việc

Và Trở Thành Một Người Có Giá Trị Hơn

Bạn Chưa Biết Phương Thức Nào Nhanh Chóng Để Đạt Được ChúngHãy Để Chúng Tôi Hỗ Trợ Cho Bạn. SEMICON

Hotline: 0972.800.931 - 0938.838.404 (Mr Long)

Từ khóa » Tổng Quan Về Ngôn Ngữ Verilog

-

Verilog – Wikipedia Tiếng Việt

-

Verilog Căn Bản: Giới Thiệu Về Ngôn Ngữ Verilog | Vi Mạch

-

(PDF) Giáo Trình Verilog HDL | Huu Nguyen Trong

-

Bài 1: Cấu Trúc Chương Trình Verilog - Tiện ích 123

-

Tổng Quan Về Verilog - Tài Liệu Text - 123doc

-

CHƯƠNG 1. TỔNG QUAN VỀ NGÔN NGỮ LẬP TRÌNH PHẦN ...

-

[Verilog]Tổng Quan Về Ngôn Ngữ Thiết Kế Phần Cứng Verilog

-

Thegioivimach - [Nhập Môn Verilog HDL] Bài 1: Tổng Quan Về...

-

Nghiên Cứu Ngôn Ngữ Verilog HDL

-

[Verilog][System Verilog] Thế Nào Là Verilog Hoặc System Verilog ...

-

[Verilog] Các Cách Mô Tả Một Mạch Tổ Hợp Với Ngôn Ngữ Verilog

-

Thiết Kế Mạch Logic Bằng Verilog - HDL - TailieuXANH